17.2.3 DS18S20的访问流程

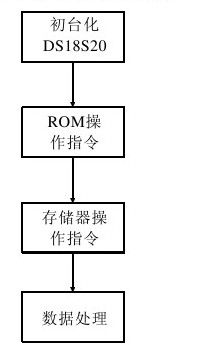

DS18S20需要严格的时序协议才能实现单总线通信。通过单总线端口访问DS18S20的流程图,如图17.5所示。

单总线协议在总线数据访问的过程中,存在几种典型的信号类型:复位脉冲、存在脉冲、写0、写1、读0和读1。其中,存在脉冲由单总线从机发出,其余均由单总线主机发出。单总线主机与DS18S20之间的任何操作都需要初始化开始。初始化时,单总线主机发出复位脉冲,单总线从机紧跟其后发出存在脉冲。存在脉冲通知单总线主机DS18S20在总线上已准备好,可以进行后续的ROM命令和存储器操作命令。

单总线主机和从机DS18S20的直接数据读写是通过前面介绍的ROM操作命令、存储器操作命令以及时间隙处理来实现的。时间隙包括写时间隙和读时间隙,下面分别对其作如下所示的介绍。

图 17.5 通过单总线访问

❑写时间隙:当单总线主机把数据线DQ从逻辑高电平拉到逻辑低电平的时候,写时间隙便开始。DS18S20需要两种写时间隙:写0时间隙和写1时间隙。当写时间隙开始后,DS18S20在15µs~60µs的时间窗口内对数据线DQ采样。如果DQ是低电平,就是写0;否则,就是写1。1-Wire主机要发出一个写1时间隙,必须把数据线DQ拉到低电平然后释放,在写时间隙开始后的15µs内,允许数据线DQ拉到高电平。单总线主机要生成一个写0时间隙,必须把数据线拉到低电平并保持60µs。

DS18S20的流程图

❑读时间隙:从DS18S20读取数据时,当单总线主机把数据线DQ从逻辑高电平拉到逻辑低电平时,读时间隙开始。数据线DQ必须至少持续1µs;从DS18S20输出的数据在读时间隙的下降沿出现后15µs内有效。此时,单总线主机必须在这15µs内停止把DQ引脚驱动为低电平,以读取数据线DQ状态。在读时间隙的结尾,数据线DQ将被外部上拉电阻拉到高电平。

由此可知,在时间隙处理中,所有写时间隙必须至少持续60µs,包括两个写周期以及至少1µs的总线恢复时间。所有读时间隙最少必须为60µs,包括两个读周期和至少1µs的总线恢复时间。